21.10.2020

# **GENERAL SPECIFICATION**

# MODULE NO. : DEM 128064U FGH

CUSTOMER P/N

| Version No. | Change Description                | Date       |

|-------------|-----------------------------------|------------|

| 0           | Original Version                  | 15.10.2020 |

| 1           | Change to Parallel+ SPI Interface | 21.10.2020 |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

|             |                                   |            |

PREPARED BY: CC

APPROVED BY: MHI

DATE: <u>21.10.2020</u>

# CONTENTS

| 1. FUNCTIONS & FEATURES2                 |

|------------------------------------------|

| 2. MECHANICAL SPECIFICATIONS2            |

| 3. EXTERNAL DIMENSIONS 3                 |

| 4. BLOCK DIAGRAM4                        |

| 5. PIN DESCRIPTION5                      |

| 6. MAXIMUM ABSOLUTE LIMIT6               |

| 7. ELECTRICAL CHARACTERISTICS 6          |

| 8. INSTRUCTION DESCRIPTION10             |

| 9. LCD LAYOUT 11                         |

| 10. IC LAYOUT 13                         |

| 11. MODULE ACCEPT QUALITY LEVEL (AQL) 13 |

| 12. RELIABILITY TEST 13                  |

| 13. LCD MODULES HANDLING PRECAUTIONS 14  |

| 14. OTHERS 14                            |

# **1. FUNCTIONS & FEATURES**

DEM 128064U Series LCD Type :

| MODULE          | LCI           | REMARK              |               |  |  |

|-----------------|---------------|---------------------|---------------|--|--|

| DEM 128064U FGH | FSTN Reflecti | ve Positive Mode    |               |  |  |

| Viewing Di      | rection       | : 6 O'clock         |               |  |  |

| Driving Scl     | neme          | : 1/64 Duty, 1/9B   | ias           |  |  |

| Power Sup       | ply Voltage   | : 3.0 V             |               |  |  |

| LCD Operation   | on Voltage    | : 10 V              |               |  |  |

| I Display Co    | ntents        | : 128 x 64 dots     |               |  |  |

| Interface       |               | : 8-bit-Parallel or | SPI Interface |  |  |

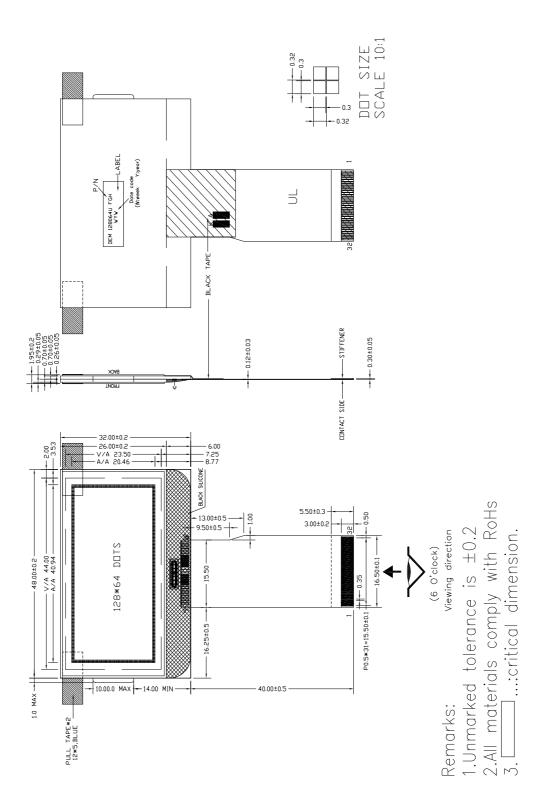

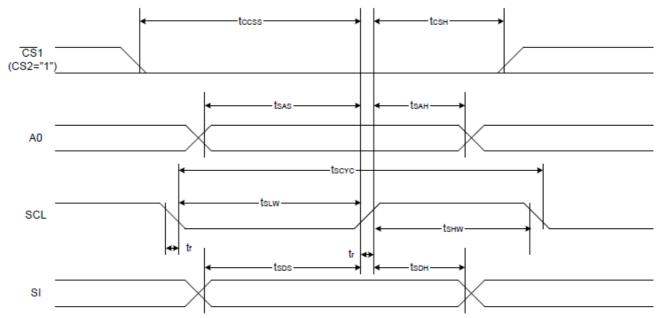

### 2. MECHANICAL SPECIFICATIONS

- Module Size

- I Viewing Area

- Active Area

- Dot Size

- I Dot Gap

: 48.00 mm x 32.00 mm x 1.95 mm

: 44.00 mm x 23.50 mm

- : 40.94 mm x 20.46 mm

- : 0.30 mm x 0.30 mm

- : 0.02 mm

# **3. EXTERNAL DIMENSIONS**

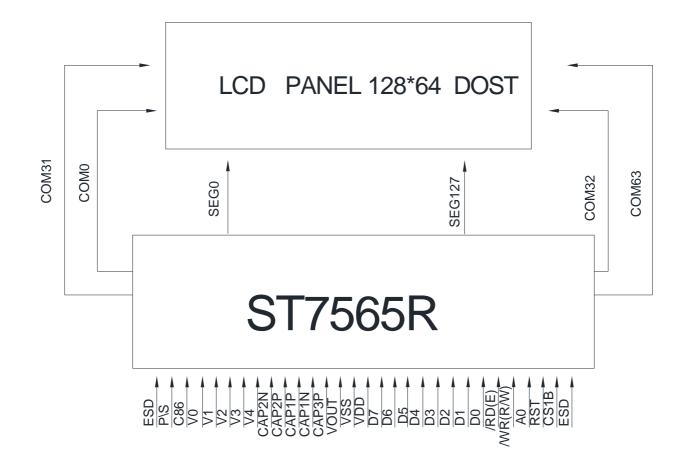

# 4. BLOCK DIAGRAM

# **5. PIN DESCRIPTION**

| Pin<br>No. | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------|------------------------|---------------------|----------------|--|--|--|--|

| 1          | ESD      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

|            |          | This pin configures the interface to be parallel mode or serial mode.<br>P/S = "H": Parallel data input/output.<br>P/S = "L": Serial data input.<br>The following applies depending on the P/S status:                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

|            |          | P/S Data/Command Data Read/Write 4-line SPI Clock                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 2          | P/S      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | "H"                                                                                                                                                                                                                                                                                                     | A0                                                                                  | D0 to D7                               | /RD, /WR               | Х                   |                |  |  |  |  |

|            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | "L"                                                                                                                                                                                                                                                                                                     | A0                                                                                  | SI (D7)                                | Write only             | SCL (D6)            |                |  |  |  |  |

|            |          | When P/S = "L", D0 to D5 must be fixed to "H".<br>/RD (E) and /WR (R/W) are fixed to either "H" or "L".<br>The serial access mode does NOT support read operation.<br>This is the MPU interface selection pin.                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 3          | C86      | C86 = "H": 6800<br>C86 = "L": 8080                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 4          | V0       | This is a multi-                                                                                                                                                                                                                                                                                                                                                                                                                                         | level po                                                                                                                                                                                                                                                                                                | wer supply for the                                                                  | liquid crystal o                       | drive. The volta       | age Supply applied  | Lis            |  |  |  |  |

| 5          | V1       | determined by t                                                                                                                                                                                                                                                                                                                                                                                                                                          | This is a multi-level power supply for the liquid crystal drive. The voltage Supply applied is determined by the liquid crystal cell, and is changed through the use of a resistive voltage divided or through changing the impedance using an op. amp. Voltage levels are determined based on Vss, and |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 6          | V2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         | npedance using ar<br>ve magnitudes sho                                              |                                        | Itage levels a         | e determined base   | ed on Vss, and |  |  |  |  |

| 7          | V3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         | -                                                                                   | Sun Bolow.                             |                        |                     |                |  |  |  |  |

| 8          | V4       | $\mathbf{v}_0 = \mathbf{v}_1 =$                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_0 \ge V1 \ge V2 \ge V3 \ge V4 \ge Vss$                                                                                                                                                                                                                                                               |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 9          | CAP2N    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 10         | CAP2P    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 11         | CAP1P    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 12         | CAP1N    | DC/DC voltage                                                                                                                                                                                                                                                                                                                                                                                                                                            | converte                                                                                                                                                                                                                                                                                                | er.                                                                                 |                                        |                        |                     |                |  |  |  |  |

| 13         | CAP3P    |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 14         | VOUT     |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 15         | VSS      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 16         | VDD      | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 17         | D7       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 18         | D6       | This is an 8-hit                                                                                                                                                                                                                                                                                                                                                                                                                                         | hi-direct                                                                                                                                                                                                                                                                                               | ional data bus tha                                                                  | t connects to                          | an 8-hit or 16         | -hit standard MPI   | I              |  |  |  |  |

| 19         | D5       | data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 20         | D4       | When the serial                                                                                                                                                                                                                                                                                                                                                                                                                                          | interfac                                                                                                                                                                                                                                                                                                | e (SPI-4) is select                                                                 | ted (P/S = "L"                         | ):                     |                     |                |  |  |  |  |

| 21         | D3       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         | I) ; D6 : the serial<br>nected to VDD or                                            |                                        | SCL).                  |                     |                |  |  |  |  |

| 22         | D2       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         | not active, D0 to I                                                                 |                                        | hiah impedan           | ce.                 |                |  |  |  |  |

| 23         | D1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                         | ,                                                                                   |                                        | 5 1                    |                     |                |  |  |  |  |

| 24         | D0       | When connects                                                                                                                                                                                                                                                                                                                                                                                                                                            | d to 900                                                                                                                                                                                                                                                                                                | 0 series MPU, thi                                                                   | o nin in trant-                        | d ac tha "/DD          | " cianal of the and | 20             |  |  |  |  |

| 25         | /RD(E)   | MPU and is LO<br>The data bus is<br>• When connect<br>MPU and is HIC                                                                                                                                                                                                                                                                                                                                                                                     | W-active<br>in an ou<br>ted to 68<br>GH-active                                                                                                                                                                                                                                                          | e.<br>utput status when<br>300 series MPU, tł<br>e.                                 | this signal is<br>his pin is trea      | "L".<br>ted as the "E" | 0                   |                |  |  |  |  |

| 26         | /WR(R/W) | This is the enable clock input terminal of the 6800 Series MPU.<br>When connected to 8080 series MPU, this pin is treated as the "/WR" signal of the 8080<br>MPU and is LOW-active.<br>The signals on the data bus are latched at the rising edge of the /WR signal.<br>• When connected to 6800 series MPU, this pin is treated as the "R/W" signal of the 6800<br>MPU and decides the access type :<br>When R/W = "H": Read.<br>When R/W = "L": Write. |                                                                                                                                                                                                                                                                                                         |                                                                                     |                                        |                        |                     |                |  |  |  |  |

| 27         | A0       | This is connect<br>determines whe<br>A0 = "H": Indica<br>A0 = "L": Indica                                                                                                                                                                                                                                                                                                                                                                                | to the le<br>other the<br>ites that<br>tes that                                                                                                                                                                                                                                                         | ast significant bit<br>data bits are data<br>D0 to D7 are disp<br>D0 to D7 are cont | a or commano<br>lay data.<br>rol data. | 1.                     |                     |                |  |  |  |  |

| 28         | RST      | When RST is se                                                                                                                                                                                                                                                                                                                                                                                                                                           | et to "L",                                                                                                                                                                                                                                                                                              | the register settin<br>erformed by the R                                            | gs are initializ                       |                        |                     |                |  |  |  |  |

| 29 | CS1B | This is the chip select signal. When CS1B = "L" |

|----|------|-------------------------------------------------|

| 30 | ESD  | Ground.                                         |

| 31 | А    | NC                                              |

| 32 | K    | NC                                              |

# 6. MAXIMUM ABSOLUTE LIMIT

| Characteristic                      | Symbol         | Conditions  | Unit |

|-------------------------------------|----------------|-------------|------|

| Power Supply Voltage                | VDD            | -0.3 ~ 3.6  | V    |

| Power supply Voltage (VDD standard) | VDD2           | -0.3 ~ 3.6  | V    |

| Power supply Voltage (VDD standard) | V0, VOUT       | -0.3 ~ 13.5 | V    |

| Power supply Voltage (VDD standard) | V1, V2, V3, V4 | -0.3 to V0  | V    |

| Operating Temperature               | TOPR           | -20 to +70  | °C   |

| Storage Temperature                 | TSTR           | -30 to +80  | °C   |

# 7. ELECTRICAL CHARACTERISTICS

### 7-1. DC Characteristics

| Item                | Symbol           | Min | Тур | Max  | Condition | Unit | Remark |

|---------------------|------------------|-----|-----|------|-----------|------|--------|

| Operating Voltage   | $V_{DD}$         | 2.7 | 3.0 | 3.3  |           | V    |        |

| LCD Driving Voltage | V <sub>LCD</sub> | 9.7 | 10  | 10.3 | -         | V    |        |

| Operating Current   | I <sub>DD</sub>  |     | TBD |      |           | mA   |        |

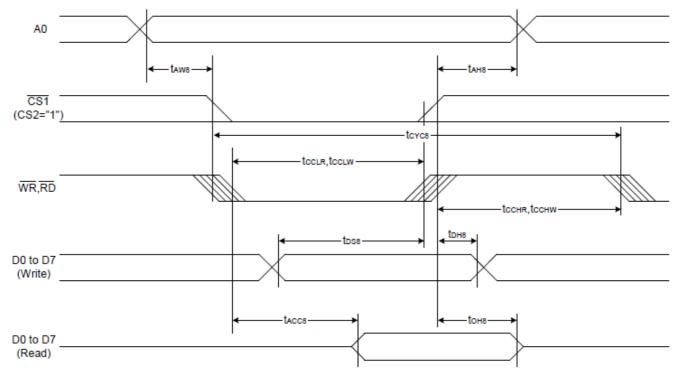

### 7-2. AC Characteristics

System Bus Read/Write Characteristics 1 (For the 8080 Series MPU)

| ltem                         | Signal   | Symbol       | Condition   | Rat  | ing  | Units            |

|------------------------------|----------|--------------|-------------|------|------|------------------|

| Item                         | Signai   | Symbol       | Condition   | Min. | Max. | Units            |

| Address hold time            |          | tah8         |             | 0    | _    |                  |

| Address setup time           | A0       | <b>t</b> aws |             | 0    | _    | ]                |

| System cycle time            |          | tcycs        |             | 240  | _    | ]                |

| Enable L pulse width (WRITE) | WR       | tccLw        |             | 80   | _    | ]                |

| Enable H pulse width (WRITE) | WK       | tсснw        |             | 80   | _    | ]                |

| Enable L pulse width (READ)  | RD       | tcclr        |             | 140  | _    | Ns               |

| Enable H pulse width (READ)  | KD       | tcchr        |             | 80   |      | ]                |

| WRITE Data setup time        |          | tosa         |             | 40   | _    | ]                |

| WRITE Address hold time      | D0 to D7 | tона         |             | 0    | -    |                  |

| READ access time             |          | tacc8        | CL = 100 pF | _    | 70   | ]                |

| READ Output disable time     | ]        | tонв         | CL = 100 pF | 5    | 50   | $\left  \right $ |

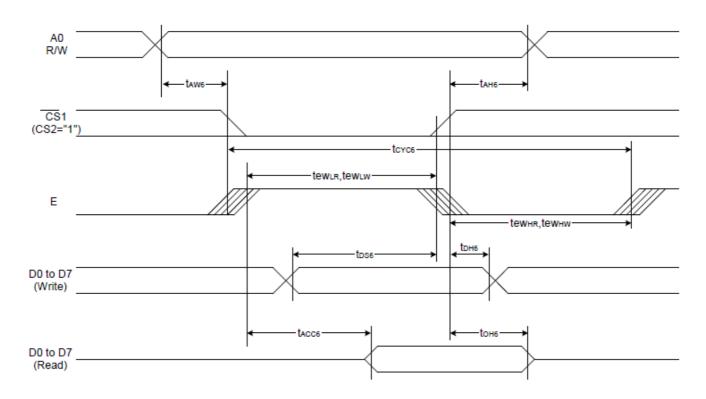

System Bus Read/Write Characteristics 2 (For the 6800 Series MPU)

| Item                         | Signal Symbol Condition |        | Condition   | Rat       | ing | Units            |

|------------------------------|-------------------------|--------|-------------|-----------|-----|------------------|

| Item                         | Sigilai                 | Symbol | Condition   | Min. Max. |     | Units            |

| Address hold time            |                         | tанв   |             | 0         | _   |                  |

| Address setup time           | A0                      | taw6   |             | 0         | _   | $\left  \right $ |

| System cycle time            |                         | tcyce  |             | 240       | _   | ]                |

| Enable L pulse width (WRITE) | WR                      | tewlw  |             | 80        | _   | ]                |

| Enable H pulse width (WRITE) | WK                      | tewнw  |             | 80        | _   | ]                |

| Enable L pulse width (READ)  | RD                      | tewlr  |             | 80        | _   | ns               |

| Enable H pulse width (READ)  | RD                      | tewhr  |             | 140       |     | ]                |

| WRITE Data setup time        |                         | tose   |             | 40        | _   | ]                |

| WRITE Address hold time      | D0 to D7                | tоне   |             | 0         | _   | ]                |

| READ access time             | 001007                  | tacce  | CL = 100 pF | _         | 70  | ]                |

| READ Output disable time     |                         | tоне   | CL = 100 pF | 5         | 50  |                  |

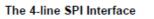

| Item                    | Signal | Symbol | Condition | Rat  | ing  | Units |

|-------------------------|--------|--------|-----------|------|------|-------|

| nem                     | Signai | Symbol | Condition | Min. | Max. | Units |

| 4-line SPI Clock Period |        | Tscyc  |           | 50   | —    |       |

| SCL "H" pulse width     | SCL    | Tshw   |           | 25   | _    |       |

| SCL "L" pulse width     | ]      | Tslw   |           | 25   | _    | 7     |

| Address setup time      | AO     | Tsas   |           | 20   | _    | 7     |

| Address hold time       | AU     | Tsah   |           | 10   | _    | ns    |

| Data setup time         | SI     | Tsds   |           | 20   | _    | 7     |

| Data hold time          | 51     | Тзрн   |           | 10   | _    | 7     |

| CS-SCL time             | CS     | Tess   |           | 20   | _    | 7     |

| CS-SCL time             | 03     | Tcsh   |           | 40   | _    |       |

# 8. INSTRUCTION DESCRIPTION

Instruction Set

| Command                                                                 |            |     |     |        | Com    | man    | d Cod        | le          |               |              |                               | Function                                                                                                                                          |

|-------------------------------------------------------------------------|------------|-----|-----|--------|--------|--------|--------------|-------------|---------------|--------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                                                                 | <b>A</b> 0 | /RD | /WR | D7     | D6     | D5     |              | D3          |               | D1           | D0                            |                                                                                                                                                   |

| (1) Display ON/OFF                                                      | 0          | 1   | 0   | 1      | 0      | 1      | 0            | 1           | 1             | 1            | 0                             | LCD display ON/OFF<br>0: OFF, 1: ON                                                                                                               |

| (2) Display start line set                                              | 0          | 1   | 0   | 0      | 1      |        | Displ        | ay st       | art a         | ddre         | SS                            | Sets the display RAM display start line<br>address                                                                                                |

| (3) Page address set                                                    | 0          | 1   | 0   | 1      | 0      | 1      | 1            | P           | age           | addr         | ess                           | Sets the display RAM page address                                                                                                                 |

| (4) Column address set<br>upper bit<br>Column address set<br>lower bit  | 0          | 1   | 0   | 0<br>0 | 0      | 0      | 1<br>0       | co<br>Le    | lumn<br>ast s | add<br>ignif | cant<br>ress<br>icant<br>ress | Sets the most significant 4 bits of the display<br>RAM column address.<br>Sets the least significant 4 bits of the display<br>RAM column address. |

| (5) Status read                                                         | 0          | 0   | 1   |        | Sta    | itus   |              | 0           | 0             | 0            | 0                             | Reads the status data                                                                                                                             |

| (6) Display data write                                                  | 1          | 1   | 0   |        |        |        |              | W           | rite d        | ata          |                               | Writes to the display RAM                                                                                                                         |

| (7) Display data read                                                   | 1          | 0   | 1   |        |        |        |              | Re          | ad d          | ata          |                               | Reads from the display RAM                                                                                                                        |

| (8) ADC select                                                          | 0          | 1   | 0   | 1      | 0      | 1      | 0            | 0           | 0             | 0            | 0<br>1                        | Sets the display RAM address SEG output<br>correspondence<br>0: normal, 1: reverse                                                                |

| (9) Display normal/<br>reverse                                          | 0          | 1   | 0   | 1      | 0      | 1      | 0            | 0           | 1             | 1            | 0                             | Sets the LCD display normal/ reverse<br>0: normal, 1: reverse                                                                                     |

| (10) Display all points<br>ON/OFF                                       | 0          | 1   | 0   | 1      | 0      | 1      | 0            | 0           | 1             | 0            | 0<br>1                        | Display all points<br>0: normal display<br>1: all points ON                                                                                       |

| (11) LCD bias set                                                       | 0          | 1   | 0   | 1      | 0      | 1      | 0            | 0           | 0             | 1            | 0                             | Sets the LCD drive voltage bias ratio<br>0: 1/9 bias, 1: 1/7 bias (ST7565R)                                                                       |

| (12) Read-modify-write                                                  | 0          | 1   | 0   | 1      | 1      | 1      | 0            | 0           | 0             | 0            | 0                             | Column address increment<br>At write: +1<br>At read: 0                                                                                            |

| (13) End                                                                | 0          | 1   | 0   | 1      | 1      | 1      | 0            | 1           | 1             | 1            | 0                             | Clear read/modify/write                                                                                                                           |

| (14) Reset                                                              | 0          | 1   | 0   | 1      | 1      | 1      | 0            | 0           | 0             | 1            | 0                             | Internal reset                                                                                                                                    |

| (15) Common output<br>mode select                                       | 0          | 1   | 0   | 1      | 1      | 0      | 0            | 0<br>1      | *             | *            | *                             | Select COM output scan direction<br>0: normal direction<br>1: reverse direction                                                                   |

| (16) Power control set                                                  | 0          | 1   | 0   | 0      | 0      | 1      | 0            | 1           | 0             | pera<br>mod  | <u> </u>                      | Select internal power supply operating mode                                                                                                       |

| (17) V₀ voltage<br>regulator internal<br>resistor ratio set             | 0          | 1   | 0   | 0      | 0      | 1      | 0            | 0           | Re            | sisto        | r ratio                       | Select internal resistor ratio(Rb/Ra) mode                                                                                                        |

| (18) Electronic volume<br>mode set<br>Electronic volume<br>register set | 0          | 1   | 0   | 1<br>0 | 0<br>0 | 0<br>E | 0<br>Electro | 0<br>onic v | 0<br>volun    | 0<br>ne va   | 1<br>alue                     | Set the V <sub>0</sub> output voltage<br>electronic volume register                                                                               |

| (19) Static indicator<br>ON/OFF                                         | 0          | . 1 | 0   | 1      | 0      | 1      | 0            | 1           | 1             | 0            | 0                             | 0: OFF, 1: ON                                                                                                                                     |

| Static indicator<br>register set                                        |            |     |     | 0      | 0      | 0      | 0            | 0           | 0             | 0            | Mode                          | Set the flashing mode                                                                                                                             |

| (20) Booster ratio set                                                  | 0          | 1   | 0   | 1      | 1      | 1      | 1            | 1           | 0             | 0            | 0                             | select booster ratio<br>00: 2x,3x,4x                                                                                                              |

|                                                                         | 0          |     | U   | 0      | 0      | 0      | 0            | 0           | 0             |              | ep-up<br>alue                 | 01: 5x<br>11: 6x                                                                                                                                  |

| (21) Power save                                                         | 0          | 1   | 0   |        |        |        |              |             |               |              | ·                             | Display OFF and display all<br>points ON compound command                                                                                         |

| (22) NOP                                                                | 0          | 1   | 0   | 1      | 1      | 1      | 0            | 0           | 0             | 1            | 1                             | Command for non-operation                                                                                                                         |

| (23) Test                                                               | 0          | 1   | 0   | 1      | 1      | 1      | 1            | *           | *             | *            | *                             | Command for IC test. Do not<br>use this command                                                                                                   |

# 9. LCD LAYOUT

9-1. ARTWORK

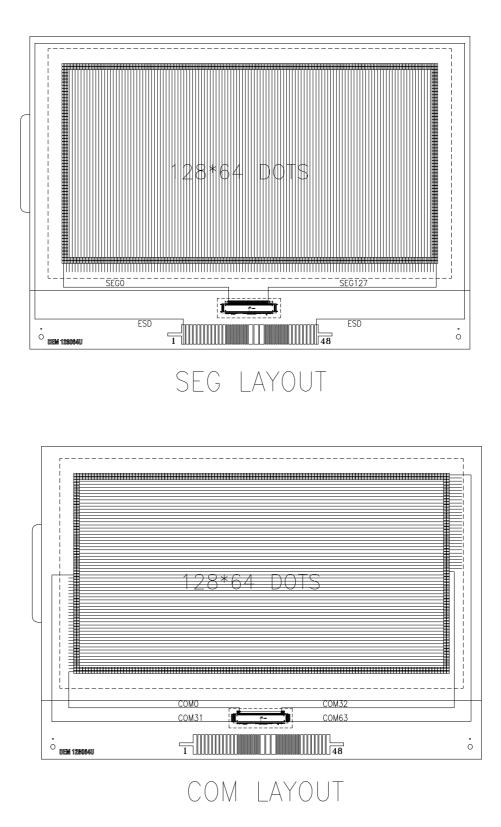

### 9-2. SEG&COM LAYOUT

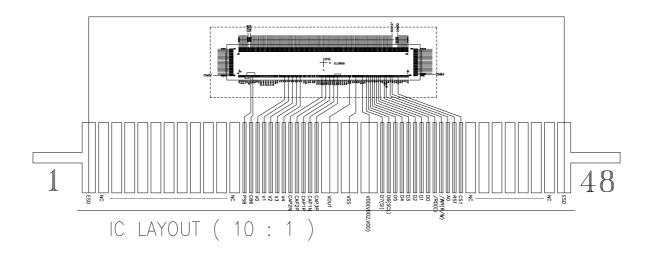

# **10. IC LAYOUT**

# 11. MODULE ACCEPT QUALITY LEVEL (AQL)

Inspection Plan: ANSI Z-1.4, Normal Inspection Level II, Single Sampling Plan.

# **12. RELIABILITY TEST**

Operating life time: Longer than 50000 hours

(at room temperature without direct irradiation of sunlight)

Reliability characteristics shall meet following requirements.

| TEMPERATURE TESTS               | NORMAL GRADE                                                                                                        |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|

| High Temperature Storage        | +80°C x 96hrs                                                                                                       |

| Low Temperature Storage         | -30°C x 96hrs                                                                                                       |

| High Temperature Operation      | +70°C x 96hrs                                                                                                       |

| Low Temperature Operation       | -20°C x 96hrs                                                                                                       |

| High Temperature, High humidity | +60°C x 90%RH x 96hrs                                                                                               |

| Thermal Shock                   | $-20^{\circ}\text{C x 30min} \longrightarrow +25^{\circ}\text{C x 10s} \longrightarrow +70^{\circ}\text{C x 30min}$ |

|                                 | 5Cycles                                                                                                             |

| Vibration Test                  | Frequency xSwing x Time                                                                                             |

|                                 | 40Hz x 4mm x 4hrs                                                                                                   |

| Drop Test                       | Drop height x Times                                                                                                 |

|                                 | 1.0m x 6times                                                                                                       |

# **13. LCD MODULES HANDLING PRECAUTIONS**

□ The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

□ If the display panel is damaged and the liquid crystal substance inside it leaks out, do not get any in your mouth. If the substance come into contact with your skin or clothes promptly wash it off using soap and water.

□ Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

□ The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarize carefully.

□ To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

-Be sure to ground the body when handling the LCD module.

-Tools required for assembly, such as soldering irons, must be properly grounded.

-To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions. -The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

$\Box$  Storage precautions

When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps. Keep the modules in bags designed to prevent static electricity charging under low temperature / normal humidity conditions (avoid high temperature / high humidity and low temperatures below  $0^{\circ}$ C). Whenever possible, the LCD modules should be stored in the same conditions in which they were shipped from our company.

### **14. OTHERS**

□ Liquid crystals solidify at low temperature (below the storage temperature range) leading to defective orientation of

liquid crystal or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subjected to a strong shock at a low temperature.

$\Box$  If the LCD modules have been operating for a long time showing the same display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. Abnormal operating status can be resumed to be normal condition by suspending use for some time. It should be noted that this phenomena does not adversely affect performance reliability.

□ To minimize the performance degradation of the LCD modules resulting from caused by static electricity, etc.

exercise care to avoid holding the following sections when handling the modules:

- Exposed area of the printed circuit board

- Terminal electrode sections