# Display Elektronik GmbH

# DATA SHEET

# LCD MODULE

# **DEM 16222 SYH**

Product specification

Version: 0

# **GENERAL SPECIFICATION**

# MODULE NO.: DEM 16222 SYH

#### CUSTOMER P/N

| VERSION NO. | CHANGE DESCRIPTION | DATE       |

|-------------|--------------------|------------|

| 0           | ORIGINAL VERSION   | 01/09/2003 |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

|             |                    |            |

PREPARED BY: ZXD DATE: 01/09/2003 APPROVED BY: MH DATE: 05/03/2004

# **CONTENTS**

| 1. FUNCTIONS & FEATURES                  | -2         |

|------------------------------------------|------------|

| 2. MECHANICAL SPECIFICATIONS             | -2         |

| 3. BLOCK DIAGRAM                         | -2         |

| 4. EXTERNAL DIMENSIONS                   | -3         |

| 5. PIN ASSIGNMENT                        | -3         |

| 6.1 PCB DRAWING AND DESCRIPTION          | -4         |

| 6.2 EXAMPLE APPLICATION                  | -5         |

| 6.3 THE MODULE NO. IS PRINTED ON THE PCB | -5         |

| 7. DISPLAY DATA RAM (DDRAM)              | -6         |

| 8. INSTRUCTION DESCRIPTION               | -6         |

| 9. INTERFACE WITH MPU IN BUS MODE        | -10        |

| 1) INTERFACE WITH 8-BIT MPU              | -10        |

| 2) INTERFACE WITH 4-BIT MPU              | -10        |

| 10. INITIALIZING BY INSTRUCTION          | -11        |

| 10-1 8-BIT INTERFACE MODE                | -11        |

| 10-2 4-BIT INTERFACE MODE                | -12        |

| 11.MAXIMUM ABSOLUTE POWER RATINGS        | -13        |

| 12.ELECTRICAL CHARACTERISTICS            | -13        |

| 12-1-1 DC CHARACTERISTICS                | -13        |

| 12-2-1 AC CHARACTERISTICS                | -15        |

| 12-2-2 WRITE MODE                        | -16        |

| 12-2-3 READ MODE                         |            |

| 13.CHARACTR GENERATOR ROM (KS0070B-00)   | -17<br>-18 |

| 15. LCD MODULES HANDLING PRECAUTIONS     | -19        |

| 14 OFFICE                                | 4.0        |

#### 1.FUNCTIONS & FEATURES

• DEM 16222-SERIES-TYPE:

| MODULE        | LCD TYPE         | LCD MODE                 |  |  |  |  |

|---------------|------------------|--------------------------|--|--|--|--|

| DEM 16222 SYH | STN Yellow/Green | Reflective Positive Mode |  |  |  |  |

• Viewing Direction : 6 o`clock

Driving Scheme : 1/16 Duty Cycle, 1/5 Bias

Power Supply Voltage : 2.7 to 5.5 Volt (typical 5.0 Volt)

$\begin{array}{lll} \bullet & V_{LCD} \; (V_{DD} - V_0) & : 4.5 \; Volt \; (typ.) \\ \bullet & Operating \; Temperature & : -20 ^{\circ}C \; to \; +70 ^{\circ}C \\ \bullet & Storage \; Temperature & : -30 ^{\circ}C \; to \; +80 ^{\circ}C \end{array}$

• Display Format : 16 x 2 Characters (5x8 dots, Format : 192 Kinds)

Internal Memory : CGROM (8,320 bits ): CGRAM (64 x 8 bits )

: DDRAM (80 x 8 bits for 80 Digits)

• Interface : Easy Interface with a 4-bit or 8-bit MPU

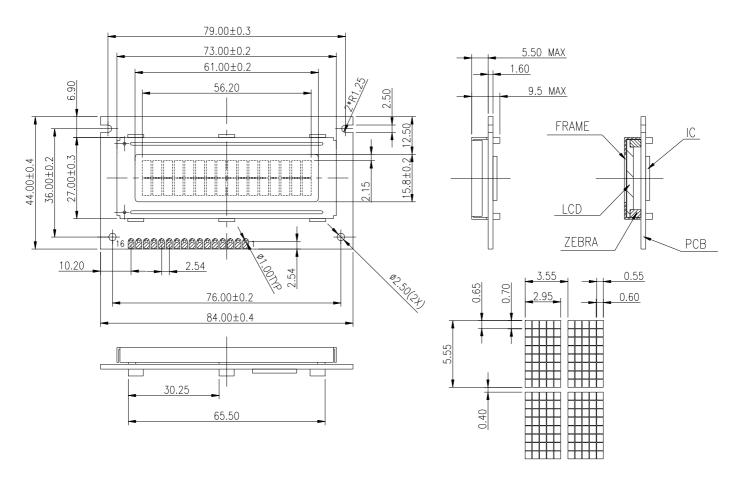

#### 2. MECHANICAL SPECIFICATIONS

Character Pitch : 3.55 (W) x 5.95 (H) mm

Character Size : 2.95 (W) x 5.55 (H)mm

• Character Font : 5 x 8 dots

Dot Size

Dot Pitch

: 0.55 (W) x 0.65 (H) mm

: 0.60 (W) x 0.70 (H) mm

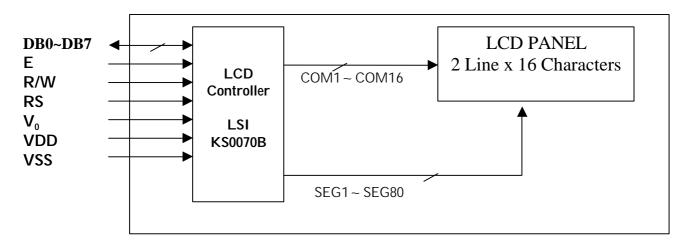

#### 3. BLOCK DIAGRAM

## 4. EXTERNAL DIMENSIONS

#### **5. PIN ASSIGNMENT**

| Pin No. | Symbol    | Function                                                              |

|---------|-----------|-----------------------------------------------------------------------|

| 1       | VSS       | Ground terminal of module.                                            |

| 2       | VDD       | Supply terminal of module 2.7V to 5.5V.                               |

| 3       | V0        | Power Supply for liquid crystal drive.                                |

| 4       | RS        | Register select RS = 0 (Instruction register) RS = 1 (Data register)  |

| 5       | R/W       | Read /Write<br>R/W = 1 (Read)<br>R/W = 0 (Write)                      |

| 6       | E         | Enable                                                                |

| 7       | DB0       |                                                                       |

| 8       | DB1       |                                                                       |

| 9       | DB2       | Bi-directional data bus, data transfer is performed once, thru DB0 to |

| 10      | DB3       | DB7, in the case of interface data. Length is 8-bits; and twice, thru |

| 11      | DB4       | DB4 to DB7 in the case of interface data length is 4-bits. Upper four |

| 12      | DB5       | bits first then lower four bits.                                      |

| 13      | DB6       |                                                                       |

| 14      | DB7       |                                                                       |

| 15      | LED + (A) | Please also refer to 6.1 PCB drawing and description.                 |

| 16      | LED - (K) | Please also refer to 6.1 PCB drawing and description.                 |

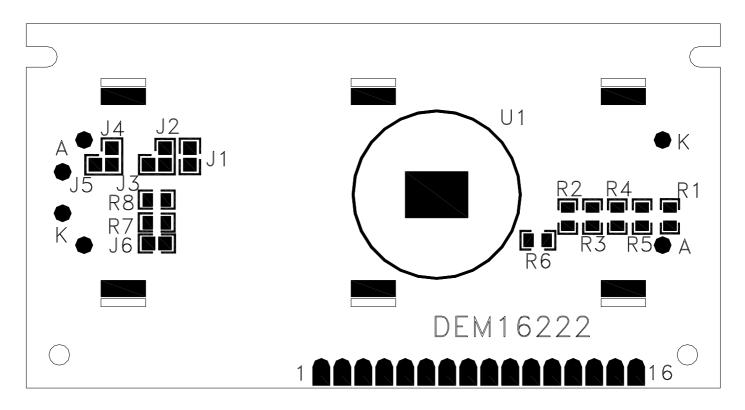

## **6.1 PCB DRAWING AND DESCRIPTION**

#### **DESCRIPTION:**

6-1-1. The polarity of the pin 15 and the pin 16:

|        | symbol J3,J5 J2, J4 |           | LED Po    | olarity |         |

|--------|---------------------|-----------|-----------|---------|---------|

| symbol | state               | 13,13     | J2, J4    | 15 Pin  | 16 Pin  |

| J2,J4  | Each solder-bridge  | Each open |           | Anode   | Cathode |

| J3,J5  | Each solder-bridge  |           | Each open | Cathode | Anode   |

6-1-2. The metal-bezel is set on ground when the J1 is closed.

6-1-3. The LED resistor can be bridged when the J6 is closed.

6-1-4. The R7 and the R8 are the LED resistor. (Not used here).

# **6.2 Example application**

6-2-1. The LED resistor should be bridged as following.

6-2-2. The 15 pin is the anode and the 16 pin is the cathode as following.

6-2-3. The 15 pin is the cathode and the 16 pin is the anode as following.

6-2-4. The metal-bezel is on ground as following.

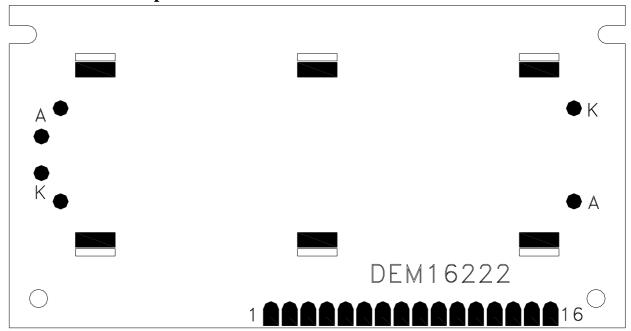

# 6.3 The module No. is printed on the PCB.

## 7. DISPLAY DATA RAM (DDRAM)

FIRST LINE SECOND LINE

|    | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | <b>■</b> -DISPLAY POSITION |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----------------------------|

| ΙE | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | <b></b> ■DDRAM ADDRESS     |

| ΙE | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |                            |

#### 8.INSTRUCTION DESCRIPTION

#### **Outline**

To overcome the speed difference between the internal clock of KS0070B and the MPU clock, KS0070B performs internal operations by storing control information to IR or DR. The internal operation is determined according to the signal from MPU, composed of read/write and data bus (refer to table 5.)

Instruction can be divided largely into four kinds:

- (1) KS0070B function set instructions (set display methods, set data length, etc.)

- (2) Address set instructions to internal RAM.

- (3) Data transfer instructions with internal RAM.

- (4) Others.

The address of the internal RAM is automatically increased or decreased by 1.

\*NOTE: During internal operation, busy flag (DB7) is read"1". Busy flag check must be preceded by the next instruction.

When you make an MPU program with checking the busy flag (DB7), it must be necessary 1/2 fosc for executing the next instruction by falling E signal after the busy flag (DB7) goes to "0".

#### **Contents**

#### 1) Clear display

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set the DDRAM addresses to "00H" in the AC (address counter). Return cursor to original status, namely, bring the cursor to the left edge on first line of the display. Make entry mode increment (I/D="1").

#### 2) Return home

|   | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ſ | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | X   |

Return home is the cursor return home instruction.

Set DDRAM address to "00H" in the address counter. Return cursor to its original site and return display to its original status, if shifted. Contents of DDRAM does not change.

#### 3) Entry mode set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | SH  |

Set the moving direction of cursor and display.

I/D: increment/decrement of DDRAM address is increased by 1.

When I/D="1", cursor/blink moves to right and DDRAM address is increased by 1.

When I/D="0", cursor/blink moves to left and DDRAM address is increased by 1.

CGRAM operates the same as DDRAM, when reading from or writing to CGRAM.

SH: shift of entire display

When DDRAM is in read (CGRAM read/write) operation or SH="0", shift of entire display is not performed.

If SH="1" and in DDRAM write operation, shift of entire display is performed according to I/D value (I/D="1": shift left, I/D="0": shift right).

#### 4) Display ON/OFF control

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |   |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   | 1 |

Control display/cursor/blink ON/OFF 1-bit register.

D: Display ON/OFF control bit

When D="1", entire display is turned on.

When D="0", display is turned off, but display data remains in DDRAM.

C: cursor or ON/OFF control bit

When C="1", cursor is turned on.

When C="0", cursor disappears in current display, but I/D register retains its data.

B: cursor blink ON/OFF control bit

When B="1", cursor blink is on, which performs alternately between all the "1" data and display characters at the cursor position.

When B="0", blink is off

#### 5) Cursor or display shift

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 1   | S/C | R/L | X   | X   |

Without writing or reading the display data, shift right/left cursor position or display.

This instruction is used to correct or search display data. (refer to table 40

During 2-line mode display, cursor moves to the 2<sup>nd</sup> line after the 40<sup>th</sup> digit of the 1<sup>st</sup> line.

Note tat display shift is performed simultaneously in all the lines.

When displayed data is shifted repeatedly, each line shifts individually.

When display shift is performed, the contents of the address counter are not changed.

Table 4. shift patterns according to S/C and R/L bits

| S/C | R/L | operation                                                                 |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Shift cursor to the left, AC is decreased by 1                            |

| 0   | 1   | Shift cursor to the right, AC is decreased by 1                           |

| 1   | 0   | Shift all the display to the left, cursor moves according to the display  |

| 1   | 1   | Shift all the display to the right, cursor moves according to the display |

#### 6) Function set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | DL  | N   | F   | X   | X   |

DL: Interface data length control bit

When DL="1", it means 8-bit bus mode with MPU.

When DL="0", it means 4-bit bus mode with MPU. So to speak, DL is a signal to select 8-bit or 4-bit bus mode. When 4- bit bus mode, it needs to transfer 4-bit data in two parts.

N: display line number control bit

When N="0", it means 1-line display mode.

When N="1", it means 2-line display mode.

F: display font type control bit

When F="0", 5 x 7 dots format display mode.

When F="1", 5 x 10 dots format display mode.

#### 7) Set CGRAM address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |  |

Set CGRAM address to AC.

THIS INSTRUCTION MAKES CGRAM data available from MPU.

#### 8) Set DDRAM address

|   | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ſ | 0  | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set DDRAM address to AC

This instruction makes DDRAM data available from MPU.

When in 1-line display mode (N=0), DDRAM address is from "00H" to "4FH".

In 2-line display mode (N=1), DDRAM address in the 1<sup>st</sup> line is from "00H" to "27H", and DDRAM address in the 2nd line is from "40H" to "67H".

#### 9) Read busy flab & address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

This instruction shows whether KS0070B is in internal operation or not. If the resultant BF is "1", it means the internal operation is in progress and your have to wait until BF is low. Then the next instruction can be performed. In this instruction your can also read the value of the address counter.

#### 10) Write data to RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM / CGRAM

The selection of RAM from DDRAM, and CGRAM, is set by the previous address set instruction: DDRAM address set, and CGRAM address set. RAM set instruction can also determine the AC direction to RAM.

After write operation, the address is automatically increased/decreased by 1, according to the entry mode.

#### 11) Read data to RAM

| _ | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM.

The selection of RAM is set by the previous address set instruction. If the address set instruction of RAM is not performed before this instruction, the data that is read first is invalid, because the direction of AC is not determined. If you read RAM data several times without RAM address set instruction before read operation, you can get correct RAM data. In the case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction; it also transfers RAM data to the output data register.

After read operation the address counter is automatically increased/decreased by 1 according to the entry mode. After CGRAM read operation, display shift may not be executed correctly.

In the case of RAM write operation, after this AC is increased/decreased by 1 like read operation. At his time, AC indicates the next address position, but your can read only the previous data by the read instruction.

# **Product Specification**

Instruction table

|                                  |    |     |     |     | Instru | action ( | Code |     |     |     |                                                                                                                        | Execution                 |

|----------------------------------|----|-----|-----|-----|--------|----------|------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Instruction                      | RS | R/W | DB7 | DB6 | DB5    | DB4      | DB3  | DB2 | DB1 | DB0 | Description                                                                                                            | time<br>(fosc=<br>270kHz) |

| Clear<br>Display                 | 0  | 0   | 0   | 0   | 0      | 0        | 0    | 0   | 0   | 1   | Write "20H" to DDRAM and set DDRAM address to "00H" from AC.                                                           | 1.53 ms                   |

| Return<br>Home                   | 0  | 0   | 0   | 0   | 0      | 0        | 0    | 0   | 1   | х   | Set DDRAM address to "00H"from AC and return cursor to its original position if shifted.                               | 1.53ms                    |

| Entry Mode set                   | 0  | 0   | 0   | 0   | 0      | 0        | 0    | 1   | I/D | SH  | Assign cursor moving direction and enable the shift of entire display.                                                 | 39us                      |

| Display<br>ON/OFF<br>Control     | 0  | 0   | 0   | 0   | 0      | 0        | 1    | D   | С   | В   | Set display (D), cursor(C), and blinking of cursor (B) on/off control bit.                                             | 39us                      |

| Cursor or<br>Display shift       | 0  | 0   | 0   | 0   | 0      | 1        | S/C  | R/L | X   | X   | Set cursor moving and display shift control bit, and the direction without changing of DDRAM data.                     | 39us                      |

| Function set                     | 0  | 0   | 0   | 0   | 1      | DL       | N    | F   | X   | X   | Set interface data length (DL:4-bit/8-bit), numbers of display line (N:1-line/2-line, display font type (F:0)          | 39us                      |

| Set<br>CGRAM<br>address          | 0  | 0   | 0   | 1   | AC5    | AC4      | AC3  | AC2 | AC1 | AC0 | Set CGRAM address in address counter.                                                                                  | 39us                      |

| Set<br>CGRAM<br>address          | 0  | 0   | 1   | AC6 | AC5    | AC4      | AC3  | AC2 | AC1 | AC0 | Set DDRAM address in address counter.                                                                                  | 39us                      |

| Read busy<br>flag and<br>address | 0  | 1   | BF  | AC6 | AC5    | AC4      | AC3  | AC2 | AC1 | AC0 | Whether during internal operation or not can be known by reading BF. The contents of address counter can also be read. | Ous                       |

| Write data<br>to RAM             | 1  | 0   | D7  | D6  | D5     | D4       | D3   | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM).                                                                            | 43us                      |

| Read data to<br>RAM              | 1  | 1   | D7  | D6  | D5     | D4       | D3   | D2  | D1  | D0  | Read data into internal RAM (DDRAM/CGRAM).                                                                             | 43us                      |

NOTE: when you make an MPU program with checking the busy flag (DB7), it must be necessary 1/2 Fosc for executing the next instruction by falling E signal after the busy flag (DB7) goes to "0".

#### 9. INTERFACE WITH MPU IN BUS MODE

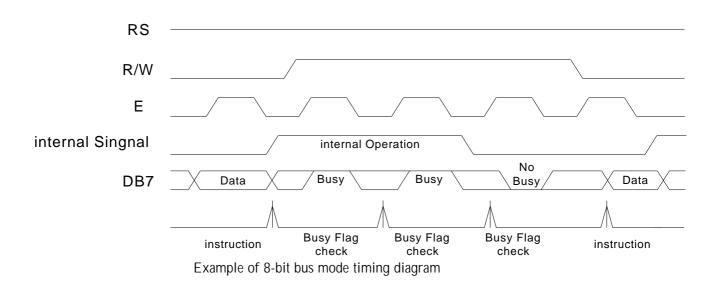

#### 1) Interface with 8-bit MPU

When interfacing data length are 8-bit, transfer is performed all at once through 8-ports, from DB0 to DB7. An example of the timing sequence is shown below.

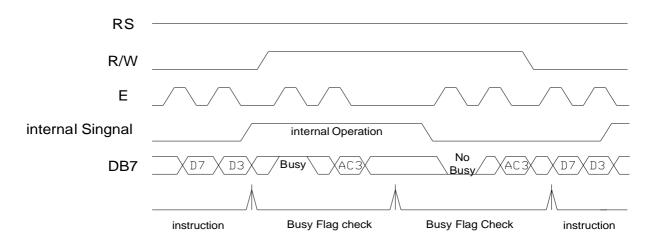

#### 2) Interface with 4-bit MPU

When interfacing data length are 4-bit, only 4 ports, from DB4 to DB7, are used as data bus.

At first, higher 4-bit (in case of 8-bit bus mode, the contents of DB4 to DB7) are transferred, and then the lower 4-bit (in case of 8-bit bus mode, the contents of DB0 to DB3) are transferred. So transfer is performed in two parts. Busy flag outputs"1"after the second transfer are ended.

Example of timing sequence is shown below.

Example of 4-bit bus mode timing diagram

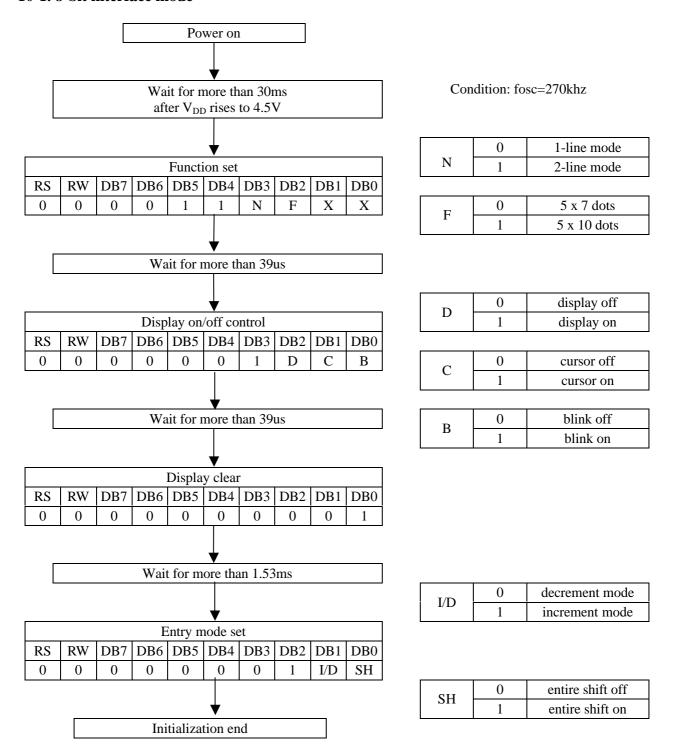

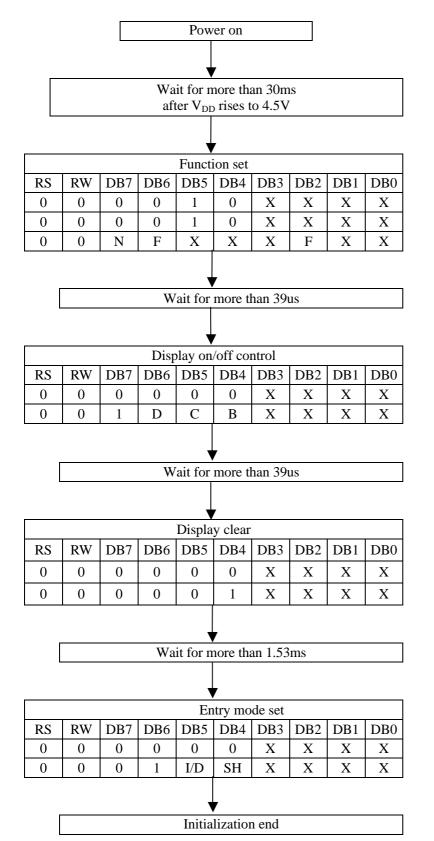

#### 10. INITIALIZING BY INSTRUCTION

#### 10-1. 8-bit interface mode

#### 10-2. 4-bit interface mode

Condition: fosc=270khz

| NI | 0 | 1-line mode |

|----|---|-------------|

| 1N | 1 | 2-line mode |

| Е  | 0 | 5 x 7 dots  |

| 1, | 1 | 5 x 10 dots |

| D | 0 | display off |

|---|---|-------------|

| D | 1 | Display on  |

| С | 0 | cursor off  |

| C | 1 | cursor on   |

| В | 0 | blink off   |

| Б | 1 | blink on    |

| I/D | 0 | decrement mode   |

|-----|---|------------------|

| I/D | 1 | increment mode   |

| SH  | 0 | entire shift off |

| SII | 1 | entire shift on  |

# 11. MAXIMUM ABSOLUTE POWER RATINGS ( $Ta = 25^{\circ}C$ )

| Item                    | Symbol          | Standard value                 | Unit |

|-------------------------|-----------------|--------------------------------|------|

| Power supply voltage(1) | $V_{DD}$        | -0.3 ~ +7.0                    | V    |

| Power supply voltage(2) | $V_{LCD}$       | $V_{DD}$ -15.0 ~ $V_{DD}$ +0.3 | V    |

| Input voltage           | V <sub>IN</sub> | $-0.3 \sim V_{DD} + 0.3$       | V    |

| Operating temperature   | Topr            | -20 ~ +70                      | °C   |

| Storage temperature     | Tstg            | -30 ~ +80                      | °C   |

## 12. ELECTRICAL CHARACTERISTICS

12-1-1 DC Characteristics ( $V_{DD} = 4.5V \sim 5.5V$ ,  $Ta = -20 \sim +70^{\circ}C$ )

| T4                              | Cb-al              | Stan                      | dard V | alue                      | Test                                                      | TT\$4    |

|---------------------------------|--------------------|---------------------------|--------|---------------------------|-----------------------------------------------------------|----------|

| Item                            | Symbol             | MIN                       | TYP    | MAX                       | Condition                                                 | Unit     |

| Operating Voltage               | $V_{\mathrm{DD}}$  | 4.5                       |        | 5.5                       |                                                           | V        |

|                                 | $I_{DD1}$          |                           | 0.7    | 1.0                       | Ceramic oscillation<br>fosc=250kHz                        |          |

| Supply Current                  | $I_{DD2}$          |                           | 0.4    | 0.6                       | Resistor oscillation external clock operation fosc=270kHz | mA       |

| Input Voltage(1)                | $V_{\rm IL1}$      | -0.3                      |        | 0.6                       |                                                           | V        |

| (except OSC1)                   | $V_{\mathrm{IH1}}$ | 2.2                       |        | $V_{ m DD}$               |                                                           | <b>v</b> |

| Input Voltage(2)                | $V_{\rm IL2}$      | -0.2                      |        | 1.0                       |                                                           | V        |

| (OSC1)                          | $V_{IH2}$          | V <sub>DD</sub> -1.0      |        | $V_{\mathrm{DD}}$         |                                                           | V        |

| Output Voltage (1)              | $V_{OL1}$          |                           |        | 0.4                       | $I_{OL}=1.2uA$                                            | V        |

| (DB0 to DB7)                    | $V_{OH1}$          | 2.4                       |        |                           | $I_{OH} = -0.205 \text{mA}$                               | <b>V</b> |

| Output Voltage (2)              | $V_{OL2}$          |                           |        | 0.1V <sub><b>DD</b></sub> | I <sub>OL</sub> =40uA                                     | V        |

| (except DB0 to DB7)             | $V_{OH2}$          | 0.9V <sub><b>DD</b></sub> |        |                           | I <sub>OH</sub> =-40uA                                    | V        |

| Voltage Drop                    | $Vd_{COM}$         |                           |        | 1                         | $IO=\pm 0.1 \text{ mA}$                                   | V        |

| voltage Diop                    | $Vd_{SEG}$         |                           |        | 1                         | 10−± 0.1 IIIA                                             | <b>V</b> |

| Input Leakage Current           | $I_{\mathrm{IL}}$  | -1                        |        | 1                         | $V_{IN}=0 V \text{ to } V_{DD}$                           | uA       |

| Input Low Current               | $I_{IN}$           | -50                       | -125   | -250                      | $V_{IN}=0V$ , $V_{DD}=5V$ (pull up)                       | uA       |

| Internal Clock<br>(external Rf) | $f_{IC}$           | 190                       | 270    | 350                       | $Rf = 91k\pm2\%$ $(V_{DD}=5V)$                            | kHz      |

|                                 | $f_{EC}$           | 150                       | 250    | 350                       |                                                           | kHz      |

| External Clock                  | Duty               | 45                        | 50     | 55                        |                                                           | %        |

|                                 | $t_R, t_F$         |                           |        | 0.2                       |                                                           | us       |

| LCD Driving Voltage             | $V_{LCD}$          | 4.6                       |        | 10.0                      | V <sub>DD</sub> -V5 (1/5, 1/4 Bias)                       | V        |

$(V_{DD} = 2.7V \sim 4.5V, Ta = -20 \sim +70^{\circ}C)$

| T                               | G 1 1              | Stan                 | dard V | alue                      | Test                                                      | TT *4    |  |

|---------------------------------|--------------------|----------------------|--------|---------------------------|-----------------------------------------------------------|----------|--|

| Item                            | Symbol             | MIN                  | TYP    | MAX                       | Condition                                                 | Unit     |  |

| Operating Voltage               | $V_{DD}$           | 2.7                  |        | 4.5                       |                                                           | V        |  |

|                                 | $I_{DD1}$          |                      | 0.3    | 0.5                       | Ceramic oscillation<br>fosc=250kHz                        |          |  |

| Supply Current                  | $I_{\mathrm{DD2}}$ |                      | 0.17   | 0.3                       | Resistor oscillation external clock operation fosc=270kHz | mA       |  |

| Input Voltage(1)                | $V_{\rm IL1}$      | -0.3                 |        | 0.4                       |                                                           | V        |  |

| (except OSC1)                   | $V_{\mathrm{IH1}}$ | $0.7V_{\mathrm{DD}}$ |        | $V_{ m DD}$               |                                                           | <b>V</b> |  |

| Input Voltage(2)                | $V_{\rm IL2}$      |                      |        | $0.2V_{\mathrm{DD}}$      |                                                           | V        |  |

| (OSC1)                          | $V_{IH2}$          | $0.7V_{DD}$          |        | $V_{ m DD}$               |                                                           |          |  |

| Output Voltage (1)              | $V_{OL1}$          |                      |        | 0.4                       | $I_{OL}=0.1$ mA                                           | V        |  |

| (DB0 to DB7)                    | $V_{OH1}$          | 2.0                  |        |                           | $I_{OH}$ =-0.1mA                                          | V        |  |

| Output Voltage (2)              | $V_{OL2}$          |                      |        | 0.2V <sub><b>DD</b></sub> | I <sub>OL</sub> =40uA                                     | V        |  |

| (except DB0 to DB7)             | $V_{OH2}$          | $0.8V_{ m DD}$       |        |                           | I <sub>OH</sub> =-40uA                                    |          |  |

| Voltage Drop                    | $Vd_{COM}$         |                      |        | 1                         | $IO=\pm 0.1 \text{ mA}$                                   |          |  |

|                                 | $Vd_{SEG}$         |                      |        | 1.5                       |                                                           |          |  |

| Input Leakage Current           | $ m I_{IL}$        | -1                   |        | 1                         | $V_{IN}=0 V \text{ to } V_{DD}$                           | uA       |  |

| Input Low Current               | $I_{IN}$           | -10                  | -50    | -120                      | $V_{IN}=0V$ , $V_{DD}=3V$ (pull up)                       | uA       |  |

| Internal Clock<br>(external Rf) | $f_{IC}$           | 190                  | 250    | 350                       | $Rf = 75k \pm 2\%$ $(V_{DD}=3V)$                          | kHz      |  |

|                                 | $f_{EC}$           | 125                  | 270    | 350                       |                                                           | kHz      |  |

| External Clock                  | Duty               | 45                   | 50     | 55                        |                                                           | %        |  |

|                                 | $t_R, t_F$         |                      |        | 0.2                       |                                                           | us       |  |

| LCD Driving Voltage             | $V_{LCD}$          | 3.0                  |        | 10.0                      | V <sub>DD</sub> -V5 (1/5, 1/4 Bias)                       | V        |  |

# **Product Specification**

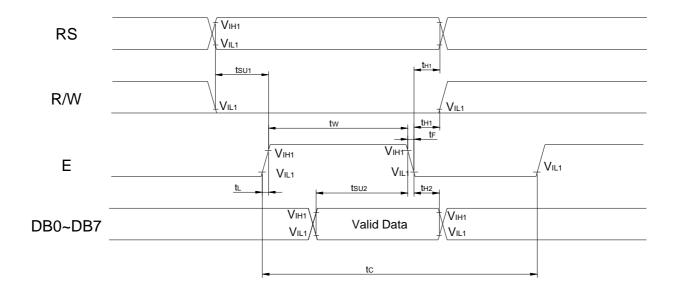

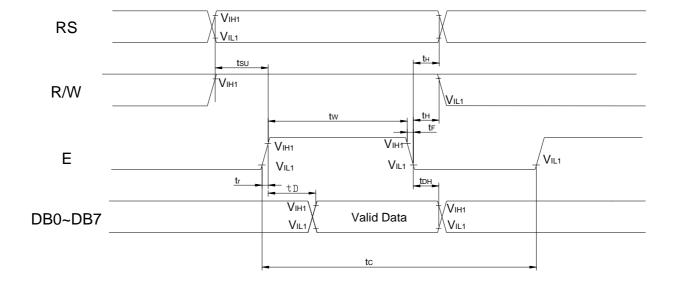

#### 12-2-1 AC Characteristics

| $(V_{DD} = 4.5V \sim 5.5V, Ta = -20 \sim +70$ | )°( | C) |

|-----------------------------------------------|-----|----|

|-----------------------------------------------|-----|----|

| Mode                   | Item                      | Symbol           | Min | Тур | Max | Unit |

|------------------------|---------------------------|------------------|-----|-----|-----|------|

|                        | E Cycle Time              | $t_{\rm C}$      | 500 |     |     |      |

|                        | E Rise/Fall Time          | $t_R, t_F$       |     |     | 25  |      |

| (1) Write Mode         | E Pulse Width (High, Low) | $t_{\rm w}$      | 220 |     |     |      |

| (refer to Figure 10.0) | R/W and RS Setup Time     | $t_{su1}$        | 40  |     |     | ns   |

|                        | R/W and RS Hold Time      | $t_{H1}$         | 10  |     |     |      |

|                        | Data Setup Time           | $t_{su2}$        | 60  |     |     |      |

|                        | Data Hold Time            | $t_{H2}$         | 10  |     |     |      |

|                        | E Cycle Time              | $t_{\rm C}$      | 500 |     |     |      |

|                        | E Rise/Fall Time          | $t_R, t_F$       |     |     | 25  |      |

| (2) Read Mode          | E Pulse Width (High, Low) | $t_{\rm w}$      | 220 |     |     |      |

| (refer to Figure 11.0) | R/W and RS Setup Time     | $t_{su}$         | 40  |     |     | ns   |

|                        | R/W and RS Hold Time      | $t_{\rm H}$      | 10  |     |     |      |

|                        | Data Out Delay Time       | $t_{\mathrm{D}}$ |     |     | 120 |      |

|                        | Data Hold Time            | $t_{DH}$         | 20  |     |     |      |

$$(V_{DD} = 2.7V \sim 4.5V, Ta = -20 \sim +70^{\circ}C)$$

| Mode                                    | Item                      | Symbol            | Min  | Тур | Max | Unit |

|-----------------------------------------|---------------------------|-------------------|------|-----|-----|------|

|                                         | E Cycle Time              | $t_{\rm C}$       | 1400 |     |     |      |

|                                         | E Rise/Fall Time          | $t_R, t_F$        |      |     | 25  |      |

| (3) Write Mode                          | E Pulse Width (High, Low) | $t_{\rm w}$       | 400  |     |     |      |

| (refer to Figure 10.0)                  | R/W and RS Setup Time     | $t_{su1}$         | 60   |     |     | ns   |

|                                         | R/W and RS Hold Time      | t <sub>H1</sub>   | 20   |     |     |      |

|                                         | Data Setup Time           | $t_{su2}$         | 140  |     |     |      |

|                                         | Data Hold Time            | $t_{H2}$          | 10   |     |     |      |

| (4) Read Mode<br>(refer to Figure 11.0) | E Cycle Time              | $t_{\rm C}$       | 1400 |     |     |      |

|                                         | E Rise/Fall Time          | $t_R, t_F$        |      |     | 25  |      |

|                                         | E Pulse Width (High, Low) | $t_{\mathrm{w}}$  | 450  |     |     |      |

|                                         | R/W and RS Setup Time     | $t_{su}$          | 60   |     |     | ns   |

|                                         | R/W and RS Hold Time      | $t_{\mathrm{H}}$  | 20   |     |     |      |

|                                         | Data Out Delay Time       | $t_{\mathrm{D}}$  |      |     | 360 |      |

|                                         | Data Hold Time            | $t_{\mathrm{DH}}$ | 5    |     |     |      |

#### 12-2-2 Write mode

#### **12-2-3 Read mode**

## 13. CHARACTER GENERATOR ROM

| Upper(4bit)  | LLLL       | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL | НГНН | HHLL | HHLH | HHHL | нннн |

|--------------|------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Lowerr(4bit) |            |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLLL         | CG RAM (1) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLLH         | (2)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLHL         | (3)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLHH         | (4)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHLL         | (5)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHLH         | (6)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHHL         | (7)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LННН         | (8)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLLL         | (1)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLLH         | (2)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLHL         | (3)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| нінн         | (4)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHLL         | (5)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHLH         | (6)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| нннг         | (7)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| нннн         | (8)        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

Character Code (DDRAM data ) **CGRAM Address CGRAM Data Pattern** number P4 P3 P2 P1 **P**0 D6 D5 D4 D3 D2 D1 D0 A5 A4 A3 A2 **P5** Pattern 1 Pattern 8

Table 3. Relationship Between character Code (DDRAM) and Character Pattern (CGRAM)

"x": don't care

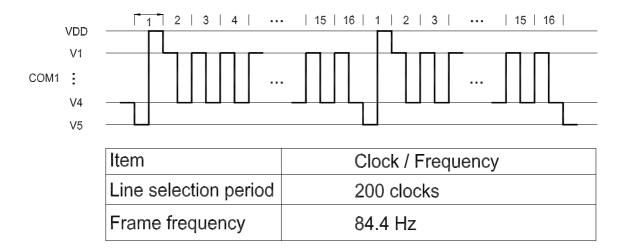

## 14. FRAME FREQUENCY (1/16 duty cycle)

# A-type Waveform

\* fosc = 270 kHz (1 clock = 3.7 us )

## 15. LCD Modules Handling Precautions

- The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- If the display panel is damaged and the liquid crystal substance inside it leaks out, do not get any in your mouth. If the substance come into contact with your skin or clothes promptly wash it off using soap and water.

- Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarize carefully.

- To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- -Be sure to ground the body when handling the LCD module.

- -Tools required for assembly, such as soldering irons, must be properly grounded.

- -To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- -The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

- Storage precautions

When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps. Keep the modules in bags designed to prevent static electricity charging under low temperature / normal humidity conditions (avoid high temperature / high humidity and low temperatures below 0°C). Whenever possible, the LCD modules should be stored in the same conditions in which they were shipped from our company.

#### 16. Others

- Liquid crystals solidify at low temperature (below the storage temperature range) leading to defective orientation of liquid crystal or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subjected to a strong shock at a low temperature.

- If the LCD modules have been operating for a long time showing the same display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. Abnormal operating status can be resumed to be normal condition by suspending use for some time. It should be noted that this phenomena does not adversely affect performance reliability.

- To minimize the performance degradation of the LCD modules resulting from caused by static electricity, etc. exercise care to avoid holding the following sections when handling the modules:

- Exposed area of the printed circuit board

- Terminal electrode sections